Projects

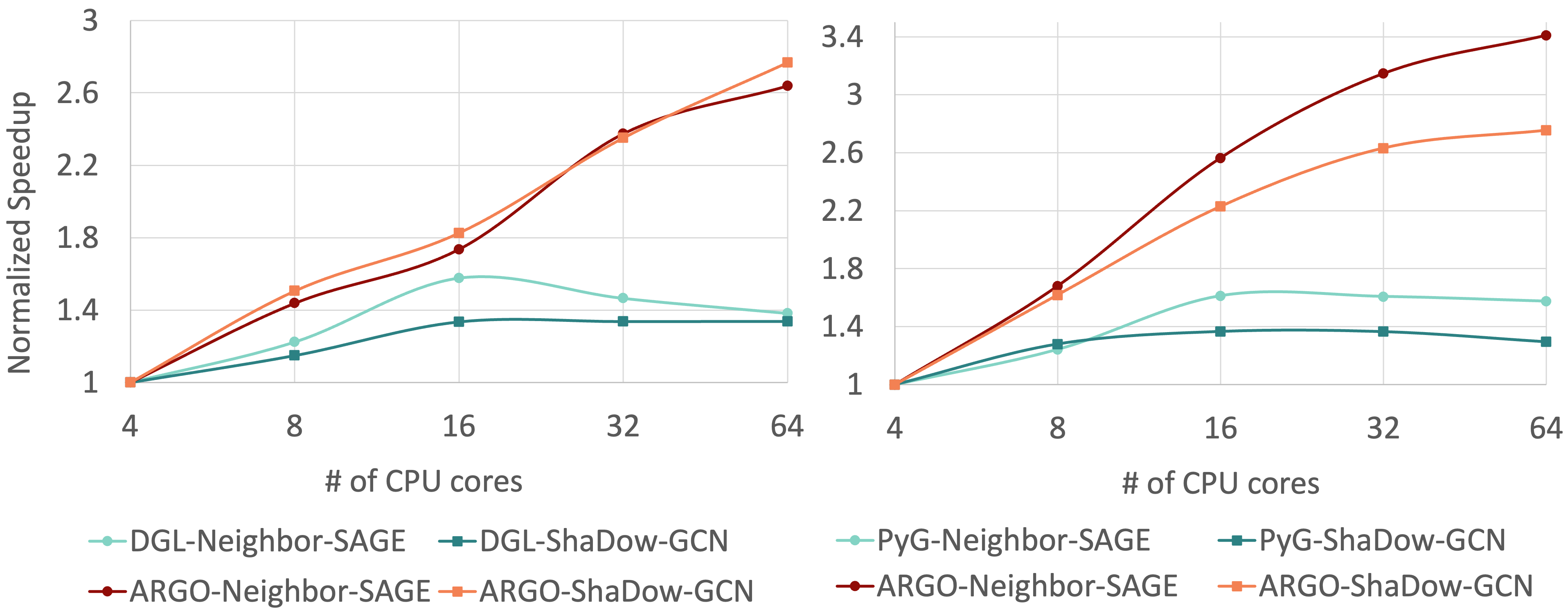

ARGO

An Auto-Tuning Runtime System that offers scalable performance for GNN training on multi-core processors.

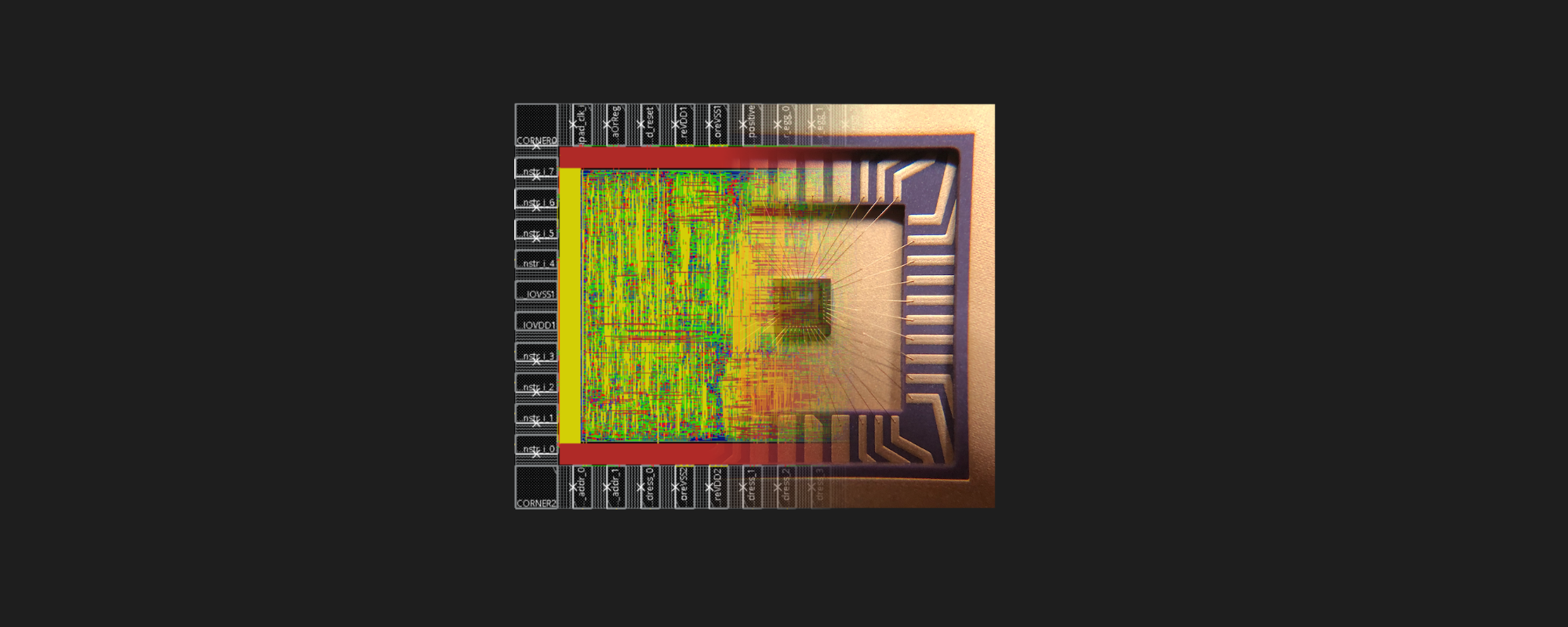

RISC-V CPU

This project implements a RISC-V CPU, from behavior level design (i.e., RTL) to tape-out.

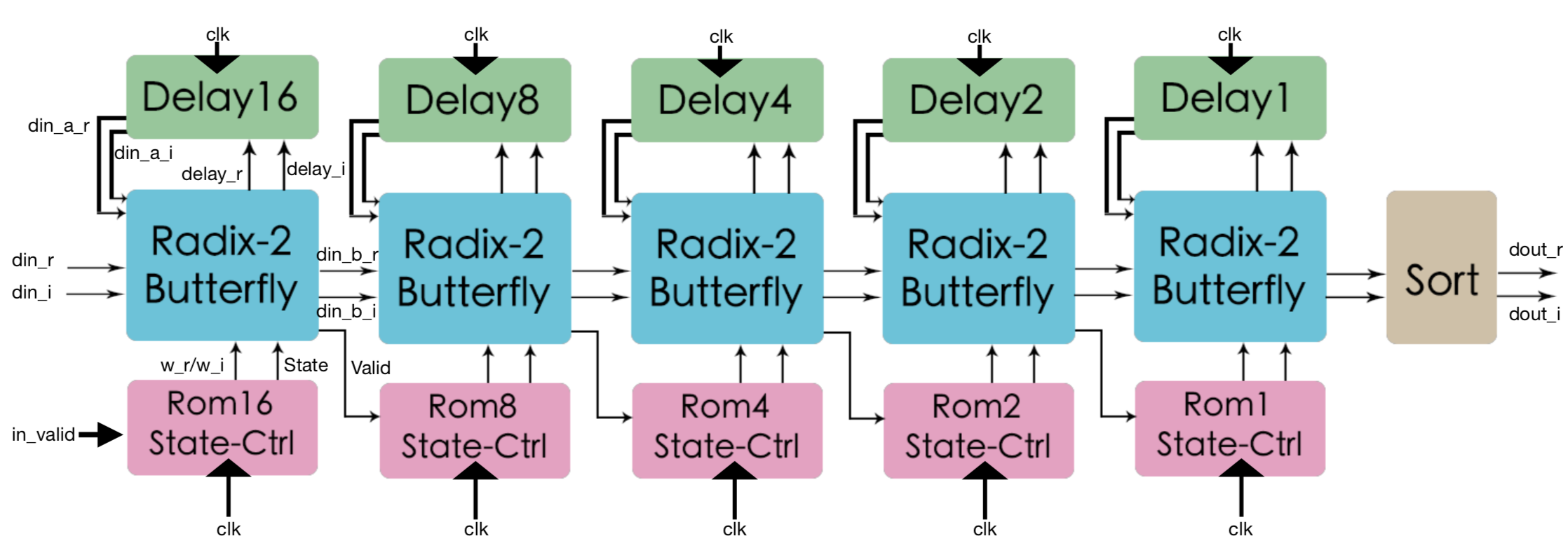

Single Path Delay 32-Point FFT Processor

A 32-point pipelined Fast Fourier Transform processor. The design is based on radix2-DIF(decimation-in-frequency) algorithm with average SNR = 58.76.